February 29, 2008

### **Revision History**

| Rev | Date              | Details                                           |

|-----|-------------------|---------------------------------------------------|

| A   | February 29, 2008 | Release of SMART PC data sheet w/SM223 controller |

|     |                   |                                                   |

|     |                   |                                                   |

SG9PCxxxSMExxx

February 29, 2008

# 64MB - 32GB Industrial Grade XceedAT Card

# 1 General Description

### 1.1 Overview

SMART is a leading independent manufacturer of memory and embedded modular sub-systems inclusive of board-level through systems level design, manufacturing, test and fulfillment services. SMART offers more than 500 standard and custom products to leading OEMs in the computer, industrial, networking and telecommunications industries worldwide.

SMART's Industrial Grade XceedAT product offering is specifically targeted at the needs of OEM markets such as networking, telecommunications and data communications applications. SMART's XceedAT products are also a natural fit for mobile and embedded computing, medical, automotive and industrial applications.

SMART's Industrial Grade XceedAT products offer reliable high performance operation in an industry standard Type 1 ultrasonic welded PC housing. They are available in capacities from 64MB to 32GB and can operate in either 3.3V or 5V hosts.

SMART Industrial Grade XceedAT products offer an advanced static wear-leveling algorithm for extending the lifespan of the products for demanding applications. SMART Industrial Grade Flash products ensure repeatable, reliable operation in Industrial OEM applications.

SMART further increases the reliability of its Industrial Grade XceedAT product offering - yielding greater than 2 Million Program/Erase cycles for most applications - by using Single Level Cell NAND Flash technology which betters comparable Multi Level Cell technology by a factor of 10X in reliability and 2X in speed.

SMART has built its foundation by providing proven technology and quality products to the most demanding Fortune 100 OEMs. SMART engineers its products to perform at the highest degree of reliability & compatibility while backing these products with outstanding services and technology expertise.

### 1.2 Features

- PC Card Standard Release 8 Compliant

- Capacity Range 64MB to 32GB

- CIS (Card Information Structure) programmed into 256 Bytes of Attribute Memory

- Low Power Dissipation

- High Performance Read Current: 60 mA

- High Performance Write Current: 60 mA

- Passive Mode: < 6 mA

- Supports Memory Mapped, I/O Mapped, and True IDE Interface Modes

- Supports up to:

- IDE PIO Mode 6

- IDE Multi-Word DMA Mode 4

- IDE Ultra DMA Mode 5

- PCMCIA Ultra DMA Mode 5

- Hardware RS-code ECC, 4 symbol/page

- Static Wear Leveling

- RoHS compliant

- Optional Industrial Temp Range -40°C to +85°C

February 29, 2008

### 1.3 Part Numbering Information

| SMART Part<br>Number | Chip<br>Density | Physical<br>Capacity | Sector Card | Head | Cylinder            | Sector<br>Track | Un-Formatted<br>Capacity |

|----------------------|-----------------|----------------------|-------------|------|---------------------|-----------------|--------------------------|

| SG9PC64SME5xxx       | 512Mb           | 64MB                 | 123,904     | 8    | 484                 | 32              | 63,438,848               |

| SG9PC128SME1xxx      | 1Gb             | 128MB                | 248,064     | 8    | 969                 | 32              | 127,008,768              |

| SG9PC256SME1xxx      | 1Gb             | 256MB                | 497,152     | 16   | 971                 | 32              | 254,541,824              |

| SG9PC512SME2xxx      | 2Gb             | 512MB                | 994,896     | 16   | 987                 | 63              | 509,386,752              |

| SG9PC1GSME4xxx       | 4Gb             | 1GB                  | 1,989,792   | 16   | 1,974               | 63              | 1,018,773,504            |

| SG9PC2GSME9xxx       | 8Gb             | 2GB                  | 3,915,072   | 16   | 3,884               | 63              | 2,004,516,864            |

| SG9PC4GSMEAxxx       | 16Gb            | 4GB                  | 7,831,152   | 16   | 7,769               | 63              | 4,009,549,824            |

| SG9PC8GSMEBxxx       | 32Gb            | 8GB                  | 15,596,784  | 16   | 15,148              | 63              | 7,985,553,408            |

| SG9PC16GSMEBxxx      | 32Gb            | 16GB                 | 31,195,136  | 16   | 16,3841             | 63              | 15,971,909,632           |

| SG9PC32GSMEBxxx      | 32Gb            | 32GB                 | 61,079,552  | 16   | 16,384 <sup>1</sup> | 63              | 31,272,730,624           |

### 1.4 Part Number Decoder

| S | <u>G</u> | <u>9</u>        | <u>PC</u> | XXX                                                             |                                                                             | <u>SME</u>          | <u>X</u>                                                               | <u>X</u>                          | <u>X</u>          | <u>X</u>           |

|---|----------|-----------------|-----------|-----------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------|-----------------------------------|-------------------|--------------------|

| R | oHS-6    | Flash<br>Memory | PCMCIA    | 64:<br>128:<br>256:<br>512:<br>1G:<br>2G:<br>4G:<br>8G:<br>16G: | 64MB<br>128MB<br>256MB<br>512MB<br>1GB<br>2GB<br>4GB<br>8GB<br>16GB<br>32GB | Controller<br>SM223 | 5: 512Mb<br>1: 1Gb<br>2: 2Gb<br>4: 4Gb<br>9: 8Gb<br>A: 16Gb<br>B: 32Gb | Blank – Commercial I – Industrial | F – Fixed<br>Disk | P – PIO;<br>No DMA |

<sup>&</sup>lt;sup>1</sup> CHS not supported at this capacity

SG9PCxxxSMExxx

# **February 29, 2008**

### **Specification Overview**

### 1.5.1 Performance

| • | Maximum Performance (PIO 6) | Read     | <u>Write</u> |

|---|-----------------------------|----------|--------------|

|   | 256MB – 16GB                | 24  MB/s | 12 MB/s      |

|   | 128MB                       | 19 MB/s  | 6 MB/s       |

|   | 64MB                        | 10  MB/s | 1.7 MB/s     |

Maximum Performance (UDMA 4)

| 256MB – 16GB | 47  MB/s | 25  MB/s |

|--------------|----------|----------|

| 128MB        | 24 MB/s  | 7  MB/s  |

| 64MB         | 10  MB/s | 1.7 MB/s |

Host Interface Transfer Rate 16MB/s

Startup Times

Sleep to Read/Write < 2.5 ms Power up to Ready < 100 ms

Command to DRQ

Read < 220 us Write < 75 us

### 1.5.2 Reliability

**MTBF** > 2,500,000 hours 1 in 10<sup>14</sup> bits, read Data Reliability **Data Retention** 10 years >2,000,000 program/erase cycles Endurance

### **1.5.3 Power**

| • | VCC     | 5.0V±10% | 3.3V±5% |

|---|---------|----------|---------|

| • | Read    | 80 mA    | 60 mA   |

| • | Write   | 70 mA    | 60 mA   |

| • | Passive | 9 mA     | 6 mA    |

### 1.5.4 Environmental

Shock 50G max. @ 11mS 15G peak to peak Vibration Operating temperature 0°C to 70°C (Commercial) -40°C to +85°C (Industrial) -65°C to 150°C Storage temperature 5% to 95% Humidity Altitude up to 80,000 ft.

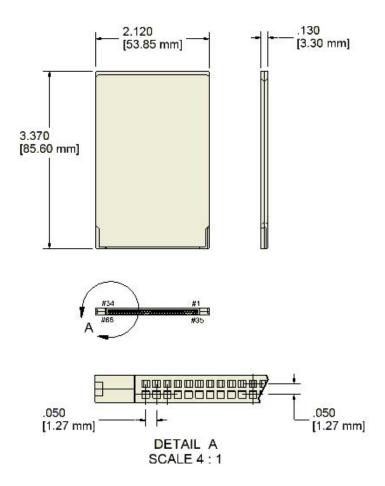

### 1.5.5 Physical Dimensions

| • | Length    | 1.433 in. (36.40 mm.) |

|---|-----------|-----------------------|

| • | Width     | 1.685 in. (42.80 mm.) |

| • | Thickness | 0.130 in. (3.30 mm.)  |

| • | Weight    | 0.36 Oz. (10.2 gm)    |

SG9PCxxxSMExxx

February 29, 2008

## **General Description**

The ATA Flash Drive contains a ATA/IDE controller and one or more flash memory devices. The Smart ATA Flash product line is offered in a UL approved Type I housing with a 68 pin PCMCIA connector. On board ATA/IDE controller interfaces with a host system allowing data to be written to and read from the flash memory devices.

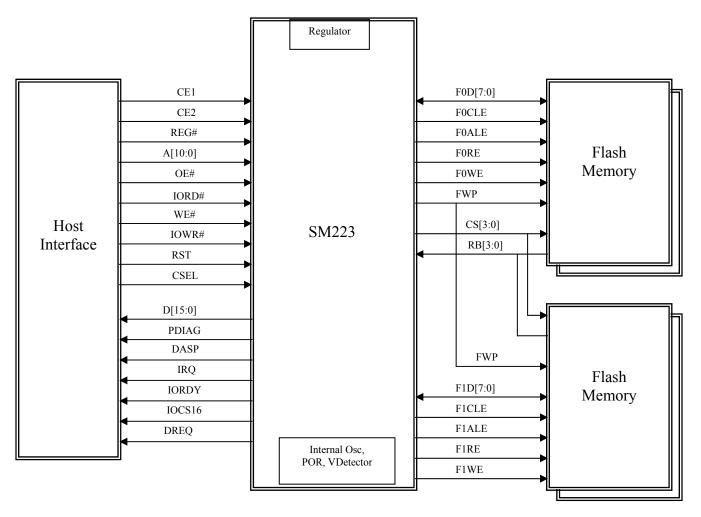

#### 2.1 **Functional Block Diagram**

#### Notes:

All the signals shown going to the flash devices come from the card controller. All the other signals including those going to the card controller come from the Card Interface.

**February 29, 2008**

## 2.2 Mechanical Specifications

February 29, 2008

### 2.3 Labels

Below are images of our standard labels for the ATA Flash card. Part number and manufacturing information are printed on the back of the card.

Front

# Industrial Grade XceedAT Card SG9PCxxxSMExxx February 29, 2008

### 3 Electrical Interface

### 3.1 Electrical Description

The Flash Cards are fully compliant with PCMCIA/ATA specification. This interface standard electrically complies with the PC Card ATA specifications, functioning in I/O Mode, Memory Mode and True IDE Modes.

Table 1 describes the I/O signals. Signals whose source is the host are designated as inputs (I) while signals that the ATA Flash Card sources are outputs (O). Bidirectional signals are designated as Input/Output (I/O). The ATA Flash Drive logic levels conform to those specified in the PCMCIA Release 8 specification. Table 2 describes the signals in the three different operating modes of the card. The three modes are Card Memory, Card I/O, and True IDE.

SG9PCxxxSMExxx

February 29, 2008

**Table 1. Pin Assignments and Pin Type**

| Card Memory Mode |                | Card I/O Mode |            |                | True IDE Mode |            |                |             |

|------------------|----------------|---------------|------------|----------------|---------------|------------|----------------|-------------|

| Pin<br>No.       | Signal<br>Name | Pin<br>Type   | Pin<br>No. | Signal<br>Name | Pin<br>Type   | Pin<br>No. | Signal<br>Name | Pin<br>Type |

| 1                | GND            | Ground        | 1          | GND            | Ground        | 1          | GND            | Ground      |

| 2                | D3             | I/O           | 2          | D3             | I/O           | 2          | D3             | I/O         |

| 3                | D4             | I/O           | 3          | D4             | I/O           | 3          | D4             | I/O         |

| 4                | D5             | I/O           | 4          | D5             | I/O           | 4          | D5             | I/O         |

| 5                | D6             | I/O           | 5          | D6             | I/O           | 5          | D6             | I/O         |

| 6                | D7             | I/O           | 6          | D7             | I/O           | 6          | D7             | I/O         |

| 7                | CE1#           | I             | 7          | CE1#           | I             | 7          | CS0#           | I           |

| 8                | A10            | I             | 8          | A10            | I             | 8          | A10            | I           |

| 9                | OE#            | I             | 9          | OE#            | I             | 9          | OE#            | I           |

| 10               | NC             | I             | 10         | A9             | I             | 10         | A9             | I           |

| 11               | A9             | I             | 11         | A8             | I             | 11         | A8             | I           |

| 12               | A8             | I             | 12         | A7             | I             | 12         | A7             | I           |

| 13               | NC             | -             | 13         | VCC            | -             | 13         | VCC            | -           |

| 14               | NC             | I             | 14         | A6             | I             | 14         | A6             | I           |

| 15               | WE#            | Ι             |            | WE#            | Ι             |            | WE#            | Ι           |

| 16               | RDY/BSY#       | О             |            | IREQ#          | О             |            | INTRQ          | О           |

| 17               | VCC            | Power         | 51         | VCC            | Power         | 51         | VCC            | Power       |

| 18               | NC             | -             | 46         | NC             | -             | 46         | NC             | -           |

| 19               | NC             | -             | 46         | NC             | -             | 46         | NC             | -           |

| 20               | NC             | -             | 46         | NC             | -             | 46         | NC             | -           |

| 21               | NC             | -             | 46         | NC             | -             | 46         | NC             | -           |

| 22               | A7             | I             |            | A7             | I             |            | A7             | I           |

| 23               | A6             | Ι             |            | A6             | I             |            | A6             | I           |

| 24               | A5             | I             | 15         | A5             | Ι             | 15         | A5             | I           |

| 25               | A4             | I             | 16         | A4             | I             | 16         | A4             | I           |

| 26               | A3             | I             | 17         | A3             | I             | 17         | A3             | I           |

| 27               | A2             | I             | 18         | A2             | Ι             | 18         | A2             | I           |

| 28               | A1             | I             | 19         | A1             | Ι             | 19         | A1             | I           |

| 29               | A0             | Ι             | 20         | A0             | Ι             | 20         | A0             | I           |

| 30               | D0             | I/O           | 21         | D0             | I/O           | 21         | D0             | I/O         |

| 31               | D1             | I/O           | 22         | D1             | I/O           | 22         | D1             | I/O         |

| 32               | D2             | I/O           | 23         | D2             | I/O           | 23         | D2             | I/O         |

| 33               | WP             | О             | 24         | IOIS16#        | О             | 24         | IOCS16#        | О           |

| 34               | GND            | Ground        | 35         | GND            | Ground        | 35         | GND            | Ground      |

SG9PCxxxSMExxx

February 29, 2008

**Table 1. Pin Assignments and Pin Type** (Continued)

| Card Memory Mode |                |          |                    | Card I/O M     | <b>Iode</b> |            | True IDE Mode  |          |  |

|------------------|----------------|----------|--------------------|----------------|-------------|------------|----------------|----------|--|

| Pin<br>No.       | Signal<br>Name | Pin Type | Pi<br>n<br>N<br>o. | Signal<br>Name | Pin Type    | Pin<br>No. | Signal<br>Name | Pin Type |  |

| 35               | GND            | Ground   | 35                 | GND            | Ground      | 35         | GND            | Ground   |  |

| 36               | CD1#           | 0        | 36                 | CD1#           | 0           | 36         | CD1#           | 0        |  |

| 37               | D11            | I/O      | 37                 | D11            | I/O         | 37         | D11            | I/O      |  |

| 38               | D12            | I/O      | 38                 | D12            | I/O         | 38         | D12            | I/O      |  |

| 39               | D13            | I/O      | 39                 | D13            | I/O         | 39         | D13            | I/O      |  |

| 40               | D14            | I/O      | 40                 | D14            | I/O         | 40         | D14            | I/O      |  |

| 41               | D15            | I/O      | 41                 | D15            | I/O         | 41         | D15            | I/O      |  |

| 42               | CE2#           | I        | 42                 | CE2#           | I           | 42         | CS1#           | I        |  |

| 43               | VS1#           | О        | 43                 | VS1#           | О           | 43         | VS1#           | О        |  |

| 44               | IORD#          | I        | 44                 | IORD#          | I           | 44         | IORD#          | Ι        |  |

| 45               | IOWR#          | I        | 45                 | IOWR#          | I           | 45         | IOWR#          | I        |  |

| 46               | NC             | -        | 46                 | NC             | -           | 46         | NC             | -        |  |

| 47               | NC             | -        | 47                 | NC             | -           | 47         | NC             | -        |  |

| 48               | NC             | -        | 48                 | NC             | -           | 48         | NC             | -        |  |

| 49               | NC             | -        | 49                 | NC             | -           | 49         | NC             | -        |  |

| 50               | NC             | -        | 50                 | NC             | -           | 50         | NC             | -        |  |

| 51               | VCC            | Power    | 51                 | VCC            | Power       | 51         | VCC            | Power    |  |

| 52               | NC             | -        | 52                 | NC             | -           | 52         | NC             | =        |  |

| 53               | NC             | -        | 53                 | NC             | -           | 53         | NC             | =        |  |

| 54               | NC             | -        | 54                 | NC             | -           | 54         | NC             | -        |  |

| 55               | NC             | -        | 55                 | NC             | -           | 55         | NC             | -        |  |

| 56               | NC             | -        | 56                 | NC             | -           | 56         | CSEL#          | I        |  |

| 57               | VS2#           | О        | 57                 | VS2#           | О           | 57         | VS2#           | O        |  |

| 58               | RESET          | I        | 58                 | RESET          | I           | 58         | RESET#         | I        |  |

| 59               | WAIT#          | О        | 59                 | WAIT#          | О           | 59         | IORDY          | O        |  |

| 60               | INPACK#        | О        | 60                 | INPACK#        | О           | 60         | DREQ           | O        |  |

| 61               | REG#           | I        | 61                 | REG#           | I           | 61         | DMACK#         | Ι        |  |

| 62               | BVD2           | I/O      | 62                 | SPKR#          | I/O         | 62         | DASP#          | I/O      |  |

| 63               | BVD1           | I/O      | 63                 | STSCHG#        | I/O         | 63         | PDIAG#         | I/O      |  |

| 64               | D8             | I/O      | 64                 | D8             | I/O         | 64         | D8             | I/O      |  |

| 65               | D9             | I/O      | 65                 | D9             | I/O         | 65         | D9             | I/O      |  |

| 66               | D10            | I/O      | 66                 | D10            | I/O         | 66         | D10            | I/O      |  |

| 67               | CD2#           | 0        | 67                 | CD2#           | 0           | 67         | CD2#           | О        |  |

| 68               | GND            | Ground   | 68                 | GND            | Ground      | 68         | GND            | Ground   |  |

SG9PCxxxSMExxx February 29, 2008

# **Table 2. Signal Description**

| Signal Name | Mode of<br>Operation | Pin Type | Pin No(s). | Description                                                                                                                                                                                    |

|-------------|----------------------|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CD1#,CD2#   |                      | 0        | 36,67      | Card Detect Outputs                                                                                                                                                                            |

|             | Card Memory<br>Mode  |          |            | These Card Detect pins are connected to ground on the Card. They are used by the host to determine that the Card is fully inserted into the socket.                                            |

|             | Card I/O Mode        |          |            | This signal is the same in this mode.                                                                                                                                                          |

|             | True IDE Mode        |          |            | This signal is the same in this mode.                                                                                                                                                          |

| IOWR#       |                      | I        | 45         | I/O Write Input                                                                                                                                                                                |

|             | Card Memory<br>Mode  |          |            | This signal is not used in this mode.                                                                                                                                                          |

|             | Card I/O Mode        |          |            | The I/O Write strobe pulse is used to clock I/O data on the Card data bus into the controller registers. The clocking will occur on the negative to positive going edge of the signal.         |

|             | True IDE Mode        |          |            | This signal has the same function as in Card I/O Mode.                                                                                                                                         |

| IORD#       |                      | I        | 44         | I/O Read Input                                                                                                                                                                                 |

|             | Card Memory<br>Mode  |          |            | This signal is not used in this mode.                                                                                                                                                          |

|             | Card I/O Mode        |          |            | This is an I/O Read strobe generated by the host. This signal gates I/O data onto the bus from the Card.                                                                                       |

|             | True IDE Mode        |          |            | This signal has the same function as in Card I/O Mode.                                                                                                                                         |

| WE#         |                      | I        | 15         | Write Enable Input                                                                                                                                                                             |

|             | Card Memory<br>Mode  |          |            | This is a signal driven by the host and used for strobing memory write data to the registers of the Card. It is also used for writing the configuration registers                              |

|             | Card I/O Mode        |          |            | In this mode, this signal is used to write the CIS and configuration registers                                                                                                                 |

|             | True IDE Mode        |          |            | In this mode, this input signal is not used and should be connected to VCC by the host.                                                                                                        |

| CSEL#       |                      | I        | 56         | Cable Select Input                                                                                                                                                                             |

|             | Card Memory<br>Mode  |          |            | This signal is not used in this mode.                                                                                                                                                          |

|             | Card I/O Mode        |          |            | This signal is not used in this mode.                                                                                                                                                          |

|             | True IDE Mode        |          |            | This signal is used to configure this device as Master or Slave. When this pin is grounded, this device is configured as Master. When this pin is tied to VCC this card is configured as Slave |

SG9PCxxxSMExxx February 29, 2008

# **Table 2. Signal Description (continued)**

| Signal Name               | Mode of<br>Operation | Pin Type | Pin No(s). | Description                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------|----------------------|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OE#                       |                      | I        | 9          | Output Enable Input                                                                                                                                                                                                                                                                                                                                                       |

|                           | Card Memory<br>Mode  |          |            | This is a strobe generated by the host interface. It is used to read data from the Card and to read the CIS and configuration registers                                                                                                                                                                                                                                   |

|                           | Card I/O Mode        |          |            | This signal is used to read the CIS and configuration registers only.                                                                                                                                                                                                                                                                                                     |

|                           | True IDE Mode        |          |            | To enable the True IDE Mode, this input should be grounded by the host.                                                                                                                                                                                                                                                                                                   |

| CE1#,CE2# /<br>CS0#, CS1# |                      | I        | 7,42       | Card Enable Inputs                                                                                                                                                                                                                                                                                                                                                        |

| CE1#, CE2#                | Card Memory<br>Mode  |          |            | These input signals are used both to select the card and to indicate to the card whether a byte or a word operation is being performed. CE2# always accesses the odd byte of the word. CE1# accesses the even byte or the odd byte of the word depending on A0 and CE2#. A multiplexing scheme based on A0, CE1#, and CE2# allows 8 bit hosts to access all data on D0-D7 |

|                           | Card I/O Mode        |          |            | This signal has the same function as in Card Memory Mode.                                                                                                                                                                                                                                                                                                                 |

| CS0#, CS1#                | True IDE Mode        |          |            | In the True IDE Mode, CS0# is the chip select for<br>the ATA Command block registers while CS1# is<br>used to select the ATA Control Block registers<br>(Alternate Status Register and the Device Control<br>Registers)                                                                                                                                                   |

| WP/IOIS16# /<br>IOCS16#   |                      | 0        | 33         | Write Protect / I/O Port 16 Output                                                                                                                                                                                                                                                                                                                                        |

| WP                        | Card Memory<br>Mode  |          |            | The card does not have a WP switch. This signal is held low after reset initialization sequence.                                                                                                                                                                                                                                                                          |

| IOIS16#                   | Card I/O Mode        |          |            | A low signal indicated that a 16 bit or odd byte only operation can be performed.                                                                                                                                                                                                                                                                                         |

| IOCS16#                   | True IDE Mode        |          |            | This signal is asserted low when the card is expecting a word data transfer cycle. This open collector line is only driven on assertion (low).                                                                                                                                                                                                                            |

| GND                       |                      | Power    | 1,34,35,68 | Ground Pin                                                                                                                                                                                                                                                                                                                                                                |

| VCC                       |                      | Power    | 17,51      | Power Supply Pin                                                                                                                                                                                                                                                                                                                                                          |

SG9PCxxxSMExxx February 29, 2008

## **Table 2. Signal Description (continued)**

| Signal Name       | Mode of<br>Operation | Pin Type | Pin No(s).                                                 | Description                                                                                                                                                                                                                                  |

|-------------------|----------------------|----------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET /<br>RESET# |                      | I        | 58                                                         | Card Reset Input                                                                                                                                                                                                                             |

| RESET             | Card Memory<br>Mode  |          |                                                            | When this pin is high, this signal resets the Flash Card. The card Reset is only at power-up if this pin is left high or open from power-up. The card is also reset when the Soft Reset bit in the Card Configuration Option Register is set |

|                   | Card I/O Mode        |          |                                                            | This signal has the same function as in Card Memory Mode.                                                                                                                                                                                    |

| RESET#            | True IDE Mode        |          |                                                            | In this mode, this input pin is active low from the host.                                                                                                                                                                                    |

| D15-D0            |                      | I/O      | 41,40,39,3<br>8,37,66,65<br>,64,6,5,4,3<br>,2,32,31,<br>30 | 16-bit Data Input/Output Bus                                                                                                                                                                                                                 |

|                   | Card Memory<br>Mode  |          |                                                            | These lines carry the Data, Commands, and Status Information between the host and the controller. D15 is the MSB of odd byte and D7 the MSB of even byte in a Word Access.                                                                   |

|                   | Card I/O Mode        |          |                                                            | This signal has the same function as in Card Memory Mode.                                                                                                                                                                                    |

|                   | True IDE Mode        |          |                                                            | All register operations occur in byte mode on D7-D0, while all data transfers are word (16-bit) accesses.                                                                                                                                    |

| A10-A0            |                      | I        | 8,11,12,22<br>,23,24,25,<br>26,27,28,<br>29                | Card Address Input Bus                                                                                                                                                                                                                       |

|                   | Card Memory<br>Mode  |          |                                                            | These addresses along with the REG# signal are used to select the following: the I/O port address registers in the card, the memory mapped port address registers, a byte in the CIS and Configuration Control and Status registers.         |

|                   | Card I/O Mode        |          |                                                            | This signal has the same function as in Card Memory Mode.                                                                                                                                                                                    |

| A2-A0             | True IDE Mode        |          |                                                            | In this mode, only A2-A0 are used to select one of the Control/Status registers. All the remaining unused address lines should be grounded by the host.                                                                                      |

SG9PCxxxSMExxx February 29, 2008

## **Table 2. Signal Description (continued)**

| Signal Name                    | Mode of<br>Operation | Pin Type | Pin No(s). | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------|----------------------|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REG# /<br>DMACK#               |                      | I        | 61         | Attribute Memory Select Input / DMA Acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| REG#                           | Card Memory<br>Mode  |          |            | This signal is used to select between Register/ Attribute Memory (REG# = low) and Common Memory (REG# = high)                                                                                                                                                                                                                                                                                                                                                                             |

| REG#                           | Card I/O Mode        |          |            | Active Low on this signal will allow accesses to I/O space                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DMACK#                         | True IDE Mode        |          |            | This is the DMA Acknowledge signal that is used for DMA data transfers between host and device. It shall be asserted by the device when it is ready to transfer data to or from the host. This signal is used in a handshake manner with DREQ.                                                                                                                                                                                                                                            |

| RDY/BSY# /<br>IREQ# /<br>INTRQ |                      | 0        | 16         | Ready/Interrupt Request Output                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RDY/BSY#                       | Card Memory<br>Mode  |          |            | This signal is set high when the card is ready to accept a new data transfer operation and held low when the card is busy. The host must have a pull-up resistor on this signal. When powering-up and when reset, the signal is held low (busy) until the card has completed the power-up or reset operation. When the signal indicates busy no operations to the card are permitted. The signal is held high whenever the card has been powered up with RESET# disconnected or asserted. |

| IREQ#                          | Card I/O Mode        |          |            | In this mode, this signal is used as interrupt request. This line is strobed low to generate a pulse mode interrupt or held low for a level mode interrupt. This is set using Configuration Option Register.                                                                                                                                                                                                                                                                              |

| INTRQ                          | True IDE Mode        |          |            | In this mode, the signal is active high request to the host.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| INPACK#/<br>DREQ               |                      | 0        | 60         | Input Port Acknowledge Output / DMA Request                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| INPACK#                        | Card Memory<br>Mode  |          |            | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| INPACK#                        | Card I/O Mode        |          |            | This signal is asserted by the card when the card is selected and is responding to an I/O read cycle. This signal is used by the host to enable the input data buffers between the host and the card.                                                                                                                                                                                                                                                                                     |

| DREQ                           | True IDE Mode        |          |            | This is the DMA Request that is used for the DMA data transfers between host and device. It shall be asserted by the device when it is ready to transfer data to or from the host. This signal is used in a handshake manner with DMACK#.                                                                                                                                                                                                                                                 |

February 29, 2008

## **Table 2. Signal Description (continued)**

| Signal Name                   | Mode of<br>Operation | Pin Type | Pin No(s). | Description                                                                                                                                                                                                                                 |

|-------------------------------|----------------------|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT# /<br>IORDY              | Орегиноп             | 0        | 59         | Extend Bus Cycle / I/O Channel Ready Output                                                                                                                                                                                                 |

| WAIT#                         | Card Memory<br>Mode  |          |            | This active low WAIT# Signal is never switched low by the card during Read/Write operations. It is used only at power –up. When both WAIT# and WE# are low at power-on, it forces a boot from the PCMCIA or IDE port rather than from Flash |

|                               | Card I/O Mode        |          |            | This signal has the same function as in Card Memory Mode.                                                                                                                                                                                   |

| IORDY                         | True IDE Mode        |          |            | This signal is held low to extend the host transfer of any host register access (read or write) when the card is not ready to respond to a data transfer request.                                                                           |

| BVD1 /<br>STSCHG# /<br>PDIAG# |                      | 0        | 63         | Battery Voltage Detect Output / Card Status<br>Changed Output / Passed Diagnostics<br>Input/Output                                                                                                                                          |

| BVD1                          | Card Memory<br>Mode  |          |            | This signal is asserted high since the card does not contain a battery.                                                                                                                                                                     |

| STSCHG#                       | Card I/O Mode        |          |            | This signal is asserted low to alert the host to changes in the RDY/BSY# and Write Protect states. Its use is controlled through the Card Configuration and Status Registers                                                                |

| PDIAG#                        | True IDE Mode        | I/O      |            | This signal is asserted by slave drive to indicate to master drive that it has completed diagnostics and is ready to provide status.                                                                                                        |

| BVD2 /<br>SPKR# /<br>DASP#    |                      | О        | 62         | Battery Voltage Detect Output / Audio<br>Waveform Output / Drive Active/Drive 1 Preset<br>Output                                                                                                                                            |

| BVD2                          | Card Memory<br>Mode  |          |            | This signal is asserted high since the card does not contain a battery                                                                                                                                                                      |

| SPKR#                         | Card I/O Mode        |          |            | This signal is asserted high since the card does not support audio.                                                                                                                                                                         |

| DASP#                         | True IDE Mode        | I/O      |            | This signal indicates that a drive is active or that a slave drive (Drive 1) is present.                                                                                                                                                    |

| VS1#, VS2#                    |                      | 0        | 43,57      | Voltage Sense Outputs                                                                                                                                                                                                                       |

|                               | Card Memory<br>Mode  |          |            | VS1# is grounded so that the Card's CIS can be read at 3.3V and VS2# is left open.                                                                                                                                                          |

|                               | Card I/O Mode        |          |            | This signal is the same in this mode.                                                                                                                                                                                                       |

|                               | True IDE Mode        |          |            | This signal is the same in this mode.                                                                                                                                                                                                       |

SG9PCxxxSMExxx

February 29, 2008

## **Table 3. Host Signal Termination**

| Item           | Signal   | Host                                                                                                        |

|----------------|----------|-------------------------------------------------------------------------------------------------------------|

| Status Signal  | RDY/BSY# | Pull-up to Vcc R $\geq$ 10 K $\Omega$                                                                       |

|                | WAIT#    | •                                                                                                           |

|                | WP       |                                                                                                             |

|                | INPACK#  | In PCMCIA modes Pull-up to Vcc R $\geq$ 10 K $\Omega$                                                       |

|                |          | In True IDE mode, if DMA operation is supported by the host,                                                |

|                |          | Pull-down to GND R $\geq$ 5.6 K $\Omega$                                                                    |

|                |          | PCMCIA / True IDE hosts switch the pull-up to pull-down in IDE mode if DMA operation is supported.          |

|                |          | The PCMCIA mode Pull-up may be left active during True IDE mode if True IDE DMA operation is not supported. |

| Voltage Sense  | VS1      | Pull up to VCC 10 K $\Omega \le R \le 100$ K $\Omega$                                                       |

|                | VS2      |                                                                                                             |

| Battery/Detect | BVD[2:1] | Pull-up R $\geq$ 50 K $\Omega$                                                                              |

February 29, 2008

### 3.2 Card Configuration

### 3.2.1 Registers and Memory Space Decoding

| CE2# | CE1# | REG# | OE# | WE# | A10 | A9 | A8-A4 | A3 | A2 | A1 | A0 | Selected Space                       |

|------|------|------|-----|-----|-----|----|-------|----|----|----|----|--------------------------------------|

| 1    | 1    | X    | X   | X   | X   | X  | XX    | X  | X  | X  | X  | Standby                              |

| X    | 0    | 0    | 0   | 1   | X   | 1  | XX    | X  | X  | X  | 0  | Configuration Register Read          |

| 1    | 0    | 1    | 0   | 1   | X   | X  | XX    | X  | X  | X  | X  | Common Memory Read (8 bit – D7-D0)   |

| 0    | 1    | 1    | 0   | 1   | X   | X  | XX    | X  | X  | X  | X  | Common Memory Read (8 bit – D15-D8)  |

| 0    | 0    | 1    | 0   | 1   | X   | X  | XX    | X  | X  | X  | 0  | Common Memory Read (16 bit – D15-D0) |

| X    | 0    | 0    | 1   | 0   | X   | 1  | XX    | X  | X  | X  | 0  | Configuration Register Write         |

| 1    | 0    | 1    | 1   | 0   | X   | X  | XX    | X  | X  | X  | X  | Common Memory Write (8 bit – D7-D0)  |

| 0    | 1    | 1    | 1   | 0   | X   | X  | XX    | X  | X  | X  | X  | Common Memory Write (8 bit – D7-D0)  |

| 0    | 0    | 1    | 1   | 0   | X   | X  | XX    | X  | X  | X  | 0  | Common Memory Write (8 bit – D7-D0)  |

| X    | 0    | 0    | 0   | 1   | 0   | 0  | XX    | X  | X  | X  | 0  | Card Information Structure Read      |

| 1    | 0    | 0    | 1   | 0   | 0   | 0  | XX    | X  | X  | X  | 0  | Invalid Access (CIS Write)           |

| 1    | 0    | 0    | 0   | 1   | X   | X  | XX    | X  | X  | X  | 1  | Invalid Access (Odd Attribute Read)  |

| 1    | 0    | 0    | 1   | 0   | X   | X  | XX    | X  | X  | X  | 1  | Invalid Access (Odd Attribute Write) |

| 0    | 1    | 0    | 0   | 1   | X   | X  | XX    | X  | X  | X  | X  | Invalid Access (Odd Attribute Read)  |

| 0    | 1    | 0    | 1   | 0   | X   | X  | XX    | X  | X  | X  | X  | Invalid Access (Odd Attribute Write) |

### 3.2.2 Configuration Registers Decoding

| CE2# | CE1# | REG# | OE# | WE# | A10 | A9 | A8-A4 | <b>A3</b> | A2 | A1 | A0 | Selected Space                             |

|------|------|------|-----|-----|-----|----|-------|-----------|----|----|----|--------------------------------------------|

| X    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0         | 0  | 0  | 0  | Configuration Option Register Read (200h)  |

| X    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0         | 0  | 0  | 0  | Configuration Option Register Write (200h) |

| X    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0         | 0  | 1  | 0  | Card Status Register Read (202h)           |

| X    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0         | 0  | 1  | 0  | Card Status Register Write (202h)          |

| X    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0         | 1  | 0  | 0  | Pin Replacement Register Read (204h)       |

| X    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0         | 1  | 0  | 0  | Pin Replacement Register Write (204h)      |

| X    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0         | 1  | 1  | 0  | Socket and Copy Register Read (206h)       |

| X    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0         | 1  | 1  | 0  | Socket and Copy Register Write (206h)      |

Note: The location of the Card Configuration Registers should always be read from the CIS since these locations may vary in future products. No Writes should be performed to the Card Attribute Memory except to the Card Configuration Register Addresses. All other attribute memory locations are reserved.

SG9PCxxxSMExxx

February 29, 2008

## 3.3 Configuration Register Description

### 3.3.1 Configuration Option Register (Address 200h in attribute memory)

The configuration Option Register is used to configure the card's interface, address decoding and interrupt and to issue a soft reset to the PC Card. This register is reset at System Power-On and by the RESET signal (after the flash card is configured in PC Card or ATA extension mode).

| Operation | В7     | В6      | В5    | B4    | В3    | B2    | B1    | В0    |

|-----------|--------|---------|-------|-------|-------|-------|-------|-------|

| R/W       | SRESET | LevlREQ | CONF5 | CONF4 | CONF3 | CONF2 | CONF1 | CONF0 |

SRESET When this bit is set to logic one, the Host interface is in the reset state.

This reset conditions is the same as a hardware or power-on reset state with the exception that this bit stays set, and the configuration as

PCMCIA remains set. This software reset condition is removed when this bit is reset to logic zero. Following a power-on or hardware reset, this bit

is cleared.

LevIREQ This bit is set to one for level mode interrupt and set to zero for pulse

mode interrupt. In pulse mode interrupt, the pulse width is at least 0.5uS. In level mode interrupt, the interrupt line is low state until the interrupt is

serviced by the system. The interrupt is driven in the inactive state.

CONF5-CONF0 Configuration Index. Set to zero by reset. It's used to select operation

mode of the Card as shown below. Please note that CONF5 and CONF4

are reserved and must be written as zero. See the table below.

| CONF5 | CONF4 | CONF3 | CONF2 | CONF1 | CONF0 | Card Mode                                |

|-------|-------|-------|-------|-------|-------|------------------------------------------|

| 0     | 0     | 0     | 0     | 0     | 0     | Memory Mapped                            |

| 0     | 0     | 0     | 0     | 0     | 1     | I/O Mapped, 16 contiguous registers      |

| 0     | 0     | 0     | 0     | 1     | 0     | Primary I/O Mapped,<br>1F0-1F7/3F6-3F7   |

| 0     | 0     | 0     | 0     | 1     | 1     | Secondary I/O Mapped,<br>170-177/376-377 |

# SG9PCxxxSMExxx

February 29, 2008

### 3.3.2 Card Status Register (Address 202h in attribute memory)

This register contains information about the card's condition.

| Operation | В7      | В6     | В5    | B4 | В3 | B2     | B1  | В0 |

|-----------|---------|--------|-------|----|----|--------|-----|----|

| Read      | Changed | SigChg | IOIs8 | 0  | 0  | PwrDwn | Int | 0  |

| Write     | 0       | SigChg | IOIs8 | 0  | 0  | PwrDwn | 0   | 0  |

Changed Indicates that one or both of the Pin Replacement Register CRdy, or

CWProt bits are set to one.

SigChg This field serves as a gate for the STSCHG# signal. When the card is con-

figured as I/O interface, and if this and the Changed field are set to one, the function shall assert STSCHG#. If this field is reset to zero, the card

shall not assert STSCHG#.

IOIs8 The host sets this bit to a one if the Card is to be configured in an 8 bit

I/O mode. The control for an 8-bit data access is built into the ATA

command set, and still must be used.

PwrDwn When the host sets this field to one, the card shall enter a power-down

state. When this field is one, the host shall not access the card. The host shall return this field to zero before attempting to access the function. The host can set this function only if the card indicates it is ready. The RDY/BSY# value becomes busy when this bit is changed. RDY/BSY# will not become ready until the power state requested has been entered. The Card automatically powers down when it is idle and powers back up when it

receives a command.

Int This bit represents the internal state of the interrupt request. This value is

available whether or not I/O interface has been configured. This signal remains true until the condition which caused the interrupt request has been serviced. If interrupts are disabled by the IEN# bit in the device con-

trol register, this bit is a zero.

SG9PCxxxSMExxx

February 29, 2008

### 3.3.3 Pin Replacement Register (Address 204h in attribute memory)

This register provides status for signals on the CF Card interface that are used in Memory Access Mode but assume a different meaning or use in I/O Mode. The register may be read and written; however, when written, the lower four bits act as a mask for changing the corresponding upper four bits.

| Operation | В7 | В6 | В5        | <b>B4</b> | В3 | B2 | B1       | В0     |

|-----------|----|----|-----------|-----------|----|----|----------|--------|

| Read      | 0  | 0  | Crdy/Bsy# | CWProt    | 0  | 0  | Mrdy/Bsy | MWProt |

| Write     | 0  | 0  | Crdy/Bsy# | CWProt    | 0  | 0  | Mrdy/Bsy | MWProt |

CRdy/Bsy# This bit is set to one when the bit RRdy/Bsy# changes state. This bit must

be cleared by the host.

CWProt This bit is set to one when the RWprot changes state. This bit must be

cleared by the host.

RRdy/Bsy# When read this bit represents the internal state of the RDY/BSY# signal.

This bit may be used to read the state of RDY/BSY# as that pin has been reallocated to use as Interrupt Request when the card is configured as I/O

interface.

RWProt This bit is always zero, since the card does not support a WP switch.

MRdy/Bsy# This bit acts as a mask for writing the corresponding CRdy/Bsy# bit.

MWProt This bit acts as a mask for writing the corresponding CWprot bit.

| Initial value of | Written | by Host | Final value of | Comment         |  |  |

|------------------|---------|---------|----------------|-----------------|--|--|

| "C" bit          | "C" Bit | "M" Bit | "C" bit        |                 |  |  |

| 0                | X       | 0       | 0              | Unchanged       |  |  |

| 1                | X       | 0       | 1              | Unchanged       |  |  |

| X                | 0       | 1       | 0              | Cleared by host |  |  |

| X                | 1       | 1       | 1              | Set by host     |  |  |

February 29, 2008

### 3.3.4 Socket and Copy Register (Address 206h in attribute memory)

This register contains additional configuration information. This register may be used by the host system to implement a substitute for the ATA Master/Slave functionality. This register is always written by the system before writing the card's Configuration Index register.

| Operation | В7       | B6 | B5         | B4 | B3 B2 B1 B0   |        |        |  |  |

|-----------|----------|----|------------|----|---------------|--------|--------|--|--|

| Read      | Reserved | C  | Copy Numbe | er | Socket Number |        |        |  |  |

| Write     | 0        | C  | Copy Numbe | er |               | Socket | Number |  |  |

Reserved This bit is reserved for future standardization. This bit must be set to zero

by the software when the register is written.

Copy Number Drive's which indicate in their CIS that they support more than one copy

of identically configured drive-cards, should have a copy number in this

field. Only 0 or 1 is allowed

Socket Number This field indicates to the Flash Drive that it is located in the nth socket.

The first socket is numbered 0.

### **3.4** Truth Tables (Transfer function tables)

### 3.4.1 Attribute Memory Table

| REG# | CE2# | CE1# | A9 | A0 | OE# | WE# | D15-D8  | D7-D0  | Function Mode                          |

|------|------|------|----|----|-----|-----|---------|--------|----------------------------------------|

| X    | 1    | 1    | X  | X  | X   | X   | High Z  | High Z | Standby                                |

| 0    | 1    | 0    | 0  | 0  | 0   | 1   | High Z  | Data   | Read CIS (8 bits)                      |

| 0    | 1    | 0    | 0  | 0  | 1   | 0   | XX      | Data   | Write CIS (8 bits)                     |

| 0    | 1    | 0    | 1  | 0  | 0   | 1   | High Z  | Data   | Read Configuration Registers (8 bits)  |

| 0    | 1    | 0    | 1  | 0  | 1   | 0   | XX      | Data   | Read Configuration Registers (8 bits)  |

| 0    | 0    | 0    | 0  | X  | 0   | 1   | Invalid | Data   | Read CIS (16 bits)                     |

| 0    | 0    | 0    | 0  | X  | 1   | 0   | XX      | Data   | Write CIS (16 bits)                    |

| 0    | 0    | 0    | 1  | X  | 0   | 1   | Invalid | Data   | Read Configuration Registers (16 bits) |

| 0    | 0    | 0    | 1  | X  | 1   | 0   | XX      | Data   | Read Configuration Registers (16 bits) |

Note: The CE# signal or both the OE# signal and the WE# signal must be de-asserted between consecutive cycle operations.

SG9PCxxxSMExxx February 29, 2008

### 3.4.2 Common Memory Table

The common memory accesses can be either 8 bit or 16 bit. The Card permits both 8 and 16 bit accesses to all of its common memory addresses.

The Card may request the host to extend the length of a memory write cycle or extend the length of a memory read cycle until data is ready by asserting the WAIT# signal at the start of the cycle.

| REG# | CE2# | CE1# | A0 | OE# | WE# | D15-D8   | D7-D0     | Function Mode           |

|------|------|------|----|-----|-----|----------|-----------|-------------------------|

| X    | 1    | 1    | X  | X   | X   | High Z   | High Z    | Standby Mode            |

| 1    | 1    | 0    | 0  | 0   | 1   | High Z   | Even Byte | Byte Read (8 bits)      |

| 1    | 1    | 0    | 1  | 0   | 1   | High Z   | Odd Byte  |                         |

| 1    | 1    | 0    | 0  | 1   | 0   | XX       | Even Byte | Byte Write (8 bits)     |

| 1    | 1    | 0    | 1  | 1   | 0   | XX       | Odd Byte  |                         |

| 1    | 0    | 0    | X  | 0   | 1   | Odd Byte | Even Byte | Word Read (16 bits)     |

| 1    | 0    | 0    | X  | 1   | 0   | Odd Byte | Even Byte | Word Write (16 bits)    |

| 1    | 0    | 1    | X  | 0   | 1   | Odd Byte | High Z    | Odd Byte Read (8 bits)  |

| 1    | 0    | 1    | X  | 1   | 0   | Odd Byte | XX        | Odd Byte Write (8 bits) |

### 3.4.3 I/O Interface Table

The I/O accesses can be either 8 bit or 16 bit. when a 16 bit port is addressed the signal IOIS16# is asserted by the PC card. Otherwise this signal is de-asserted. If on the other hand, when a 16-bit transfer is attempted and this signal is not asserted, the host must generate a pair of 8-bit references to access the even and odd bytes. The Card may request the host to extend the length of a memory write cycle or extend the length of a memory read cycle until data is ready by asserting the WAIT# signal at the start of the cycle.

| REG# | CE2# | CE1# | A0 | IORD# | IOWR# | D15-D8   | D7-D0     | Function Mode                 |

|------|------|------|----|-------|-------|----------|-----------|-------------------------------|

| X    | 1    | 1    | X  | X     | X     | High Z   | High Z    | Standby Mode                  |

| 0    | 1    | 0    | 0  | 0     | 1     | High Z   | Even Byte | Byte Input Access (8 bits)    |

| 0    | 1    | 0    | 1  | 0     | 1     | High Z   | Odd Byte  |                               |

| 0    | 1    | 0    | 0  | 1     | 0     | XX       | Even Byte | Byte Output Access (8 bits)   |

| 0    | 1    | 0    | 1  | 1     | 0     | XX       | Odd Byte  |                               |

| 0    | 0    | 0    | 0  | 0     | 1     | Odd Byte | Even Byte | Word Input Access (8 bit)     |

| 0    | 0    | 0    | 0  | 1     | 0     | Odd Byte | Even Byte | Word Output Access (8 bit)    |

| 1    | X    | X    | X  | 0     | 1     | XX       | XX        | I/O Read Inhibit              |

| 1    | X    | X    | X  | 1     | 0     | High Z   | High Z    | I/O Write Inhibit             |

| 0    | 0    | 1    | X  | 0     | 1     | Odd Byte | High Z    | Odd Byte Input only (8 bits)  |

| 0    | 0    | 1    | X  | 1     | 0     | Odd Byte | XX        | Odd Byte Output only (8 bits) |

February 29, 2008

#### 3.4.4 True IDE Mode Table

The Card can be configured in a True IDE Mode of operation. The Card can be configured in this mode only when the OE# signal is grounded by the host during the power off to power on cycle. In this True IDE Mode the Card protocol and configuration are disabled and only I/O operations to the task file and Data Registers are allowed. In this mode no memory or attribute registers are accessible to the host.

Removing PCMCIA Card and re-inserting the card while the host is powered-on will reconfigure the card into ATA mode from the original True IDE mode. To configure the card in the True IDE mode, the socket must be powered cycled with the Card inserted and the OE# asserted.

| CS1# | CS0# | A2-A0 | IORD# | IOWR# | D15-D8       | D7-D0         | Function Mode          |

|------|------|-------|-------|-------|--------------|---------------|------------------------|

| 0    | 0    | X     | X     | X     | High Z       | High Z        | Invalid                |

| 1    | 1    | X     | X     | X     | High Z       | High Z        | Standby Mode           |

| 1    | 0    | 1-7h  | 1     | 0     | XX           | Data In       | Task File Write        |

| 1    | 0    | 1-7h  | 0     | 1     | High Z       | Data Out      | Task File Read         |

| 1    | 0    | 0     | 1     | 0     | Odd Byte in  | Even Byte in  | Data Register Write    |

| 1    | 0    | 0     | 0     | 1     | Odd Byte out | Even Byte out | Data Register Read     |

| 0    | 1    | 6h    | 1     | 0     | XX           | Control In    | Control Register Write |

| 0    | 1    | 6h    | 0     | 1     | High Z       | Status Out    | All Status Read        |

February 29, 2008

## 3.5 ATA Specific Register Mapping

The Card can be configured as a high performance I/O device through

- a. Standard PC-AT disk I/O address spaces 1F0h~1F7h, 3F6h~3F7h (primary), 170h~177h, 376h~377h (secondary) with IRQ14 (or other available IRQ).

- b. Any system decoded 16 byte I/O block using any available IRQ.

- c. Memory Space.

The communication to or from the Card is done using the Task File registers which provide all the necessary registers for control and status information. The Card interface connects peripherals to the host using four register mapping methods. The following is a detailed description of these methods:

|              | Standard Configurations |                      |        |                                    |  |  |  |  |  |

|--------------|-------------------------|----------------------|--------|------------------------------------|--|--|--|--|--|

| Config Index | I/O or Memory           | Address              | Drive# | Description                        |  |  |  |  |  |

| 0 & 8        | Memory                  | 0-Fh, 400-7FFh       | 0      | Memory Mapped                      |  |  |  |  |  |

| 1 & 9        | I/O                     | Xx0-xxFh             | 0      | I/O Mapped 16 contiguous registers |  |  |  |  |  |

| 2 & Ah       | I/O                     | 1F0h-1F7h, 3F6h-3F7h | 0      | Primary I/O Mapped Drive 0         |  |  |  |  |  |

| 2 & Ah       | I/O                     | 1F0h-1F7h, 3F6h-3F7h | 1      | Primary I/O Mapped Drive 1         |  |  |  |  |  |

| 3 & Bh       | I/O                     | 1F0h-1F7h, 3F6h-3F7h | 0      | Secondary I/O Mapped Drive 0       |  |  |  |  |  |

| 3 & Bh       | I/O                     | 1F0h-1F7h, 3F6h-3F7h | 1      | Secondary I/O Mapped Drive 1       |  |  |  |  |  |

SG9PCxxxSMExxx February 29, 2008

# 3.5.1 Memory Mapped Addressing

When the Card registers are accessed via memory references, the registers appear in the common memory space window: 0~2K bytes as follows:

| REG# | A10 | A9-A4 | A3 | A2 | A1 | A0 | Offset | OE# = 0                | WE# = 0                | Notes |

|------|-----|-------|----|----|----|----|--------|------------------------|------------------------|-------|

| 1    | 0   | X     | 0  | 0  | 0  | 0  | 0      | Even RD Data           | Even WR Data           | 1     |

| 1    | 0   | X     | 0  | 0  | 0  | 1  | 1      | Error                  | Features               | 2     |

| 1    | 0   | X     | 0  | 0  | 1  | 0  | 2      | Sector Count           | Sector Count           |       |

| 1    | 0   | X     | 0  | 0  | 1  | 1  | 3      | Sector No.             | Sector No.             |       |

| 1    | 0   | X     | 0  | 1  | 0  | 0  | 4      | Cylinder Low           | Cylinder Low           |       |

| 1    | 0   | X     | 0  | 1  | 0  | 1  | 5      | Cylinder High          | Cylinder High          |       |

| 1    | 0   | X     | 0  | 1  | 1  | 0  | 6      | Select Card/Head       | Select Card/Head       |       |

| 1    | 0   | X     | 0  | 1  | 1  | 1  | 7      | Status                 | Command                |       |

| 1    | 0   | X     | 1  | 0  | 0  | 0  | 8      | Duplicate Even RD Data | Duplicate Even WR Data | 2     |

| 1    | 0   | X     | 1  | 0  | 0  | 1  | 9      | Duplicate Odd RD Data  | Duplicate Odd WR Data  | 2     |

| 1    | 0   | X     | 1  | 1  | 0  | 1  | D      | Duplicate Error        | Duplicate Feature      | 2     |

| 1    | 0   | X     | 1  | 1  | 1  | 0  | Е      | Alternate Status       | Device Control         |       |

| 1    | 0   | X     | 1  | 1  | 1  | 1  | F      | Drive Address          | Reserved               |       |

| 1    | 1   | X     | X  | X  | X  | 0  | 8      | Even RD Data           | Even WR Data           | 3     |

| 1    | 1   | X     | X  | X  | X  | 1  | 9      | Odd RD Data            | Odd WR Data            | 3     |

#### Notes:

- 1. Register 0 is accessed with CE1# and CE2# low as a word register on the combined odd data bus and even data bus. This register may also be accessed by a pair of byte accesses to the offset 0 with CE1# low and CE2# high. Note that the address space of this word register overlaps the address space of the Error/Feature byte-wide registers that lie at offset 1. When accessed twice at byte register with CE1# low, the first to be accessed is the even byte of the word and the second byte accessed is the odd byte of the equivalent word access. A byte access to register 0 with CE1# high and CE2# low accesses the error (when read) or feature (when written) register.

- 2. Register at offset 8, 9 and D are non-overlapping duplicates of the registers at offset 0 and 1. Therefore, if the registers are byte accessed in the order 9 and then 8 the data will be transferred odd byte then even byte. Repeated byte accesses to register 8 or 0 will access consecutive (even then odd) bytes from the data buffer. Repeated word accesses to register 8, 9, or 0 will access consecutive words from the data buffer. Repeated byte accesses to register 9 are not supported. However, repeated alternating byte accesses to registers 8 then 9 will access consecutive (even then odd) bytes from the data buffer. Byte accesses to register 9 access only the odd byte of the data.

- 3. Accesses to even addresses between 400h and 7FFh access register 8. Accesses to odd addresses between 400h and 7FFh access register 9. This 1K byte memory window to the data register is provided so that hosts can perform memory to memory block moves to the data register when the register lies in memory space. Some hosts, such as the X86 processors, must increment both the source and destination addresses when executing the memory to memory block move instruction. Some Card adapters also have auto incrementing logic embedded within them. This address window allows these hosts and adapters to function efficiently. Note that this entire window accesses the Date Register FIFO and does not allow random access to the data buffer within the PC Card.

SG9PCxxxSMExxx February 29, 2008

### 3.5.2 Contiguous I/O Mapped Addressing

When the system decodes a contiguous block of I/O registers to select the CF Card, the registers are accessed in the block of I/O space decoded by the system as follows:

| REG# | A3 | A2 | A1 | A0 | Offset | IORD# = 0              | IOWR# = 0              | Notes |